|

|

|

I am a Masters Student in the department of Electrical Engineering and Information Technology (D-ITET) at ETH Zurich. I got my Bachelor's in Electrical Engineering from the Indian Institute of Technology (IIT) Madras in June 2023. My research interests lie in Computer Architecture, VLSI Design, Parallel Processing, Hardware Accelerators, In-Memory Computing, and Deep Learning. Recent explosive growth in data availability ignited the need for robust and efficient architectures, confronting the age-old Von Neumann Bottleneck. Research in Processor and Memory Technologies, Domain-Specific Architectures, 3D ICs, and more, collaboratively address these challenges. I am highly interested in exploring and contributing to such real-world solutions. I am currently working on a Semester Thesis under Prof. Dr. Luca Benini at the Integrated Systems Laboratory (IIS), ETH Zurich. Project Title: A RISC-V ISA Extension for Scalar Chaining in Snitch Besides all of that, I love to draw and paint! I also enjoy reading and music. Find some of my artwork and recent reads here. Contact: Email and Phone: +41 76 216 68 83. ~ CV | Google Scholar | Github | LinkedIn | ~ |

|

Nov 2022 - May 2023 Worked under Prof. Kamakoti Veezhinathan on 'Extending RISCV Vector ISA Support to the SHAKTI C-Class Microprocessor'. Engineering configurable Vector Functional Units to integrate in the processor pipeline. |

|

Sep 2022 - Jan 2023 Worked under Prof. Sparsh Mittal on 'Adding Matrix-Multiply Support to RISCV ISA'. Aimed to implement Matrix-Multiply Extensions and Approximate Instructions to accelerate AI-related Workloads. Benchmarked against RISCV Scalar and Vector-based implementations; simulating using Gem5 and Spike. |

|

May 2022 - Aug 2022 Worked on power optimization in the GPU submodules as a member of the GPU Design Team. Developed a Python-based framework to perform retention flop list analysis to identify potential redundant flops. Can be deployed over any design submodule and serves as a novel power curtailment technique. |

|

Mar 2022 - May 2022 Implemented Discrete Cosine Transform (DCT) in Hardware using Bluespec Verilog to accelerate H.264 Video Codec Module in the SHAKTI C-Class Processor. Reduced the computational latency by employing Butterfly architecture-based fast DCT algorithm. Fastened the implementation with a cosine look-up table and fixed-point operations, meeting the design requirements. |

|

Aug 2021 - Jan 2022 Studied the Hardware Security aspects of Deep Neural Networks, specifically Adversarial Robustness of Vision Transformers to attacks like FGSM, One-Pixel, and Bit-Flips. Performed Literature Review in 'Deep Learning for Underwater Image classification' published in 2022 IEEE Transactions on Neural Networks and Learning Systems. |

|

Apr 2020 - Apr 2022 Managed a 3-Tier Team of 50+ Electronics Enthusiasts and organized several club sessions and activites across campus. Project Head for the Mountable Heads-up Display for Helmets project that assists bikers in hassle-free navigation through traffic. Taught 40+ participants the concepts of Parallel Programming (OpenMP), CUDA, and RTOS at Shaastra (Annual Technical Fest of IITM) 2022. |

| S. Mittal, S. Srivastava, and J. P. Jayanth, "A Survey of Deep Learning Techniques for Underwater Image Classification," in IEEE Transactions on Neural Networks and Learning Systems DOI |

|

Apr 2022 - Jun 2022 Designed an SRAM-based IMC Engine that performs Multiply and Accumulate with a MAC range of 128. Constructed carefully-sized Charge and Current-based SRAM Cells (with Decoupled Read-Write). Achieved 98% accuracy with IMC Engine tuned on MNIST Dataset, employing 8-bit fixed-point inputs and weights. |

|

Apr 2022 - May 2022 Accelerated the static Mandelbrot Fractal Image Generation on an FPGA using HLS C. Attained 3X Speedup over C-based software implementation, analyzing several HLS Pragmas and parameters like word lengths, memory types, and data I/O. Utilized PYNQ framework to interface PYNQ-Z1 FPGA and AXI4 Stream Protocol for data I/O. |

|

Nov 2021 - Dec 2021 Achieved 2X Speedup on accelerating the Advanced Encryption Standard (AES) algorithm on an Artix 7 FPGA using Verilog HDL. Interfaced the design with Microblaze Soft IP Core on Xilinx Vivado, providing I/O through C code using Vitis IDE. |

|

Nov 2021 - Dec 2021 Designed the Schematic and Layout of an 8-bit CSM, with and without pipelining on GNU Electric. Simulated and Validated the DRC & LVS clean design using LTSpice and performed RC Extraction on the complete layout for critical path delay analysis. |

|

Sep 2021 Built a 5-Stage pipelined RISCV ISA-based 32-bit Processor with Hazard Detection and Data Forwarding Units, coded using Verilog HDL. |

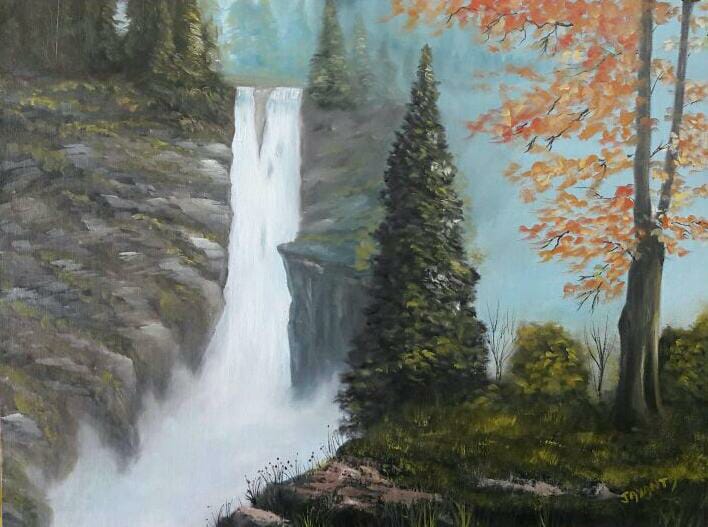

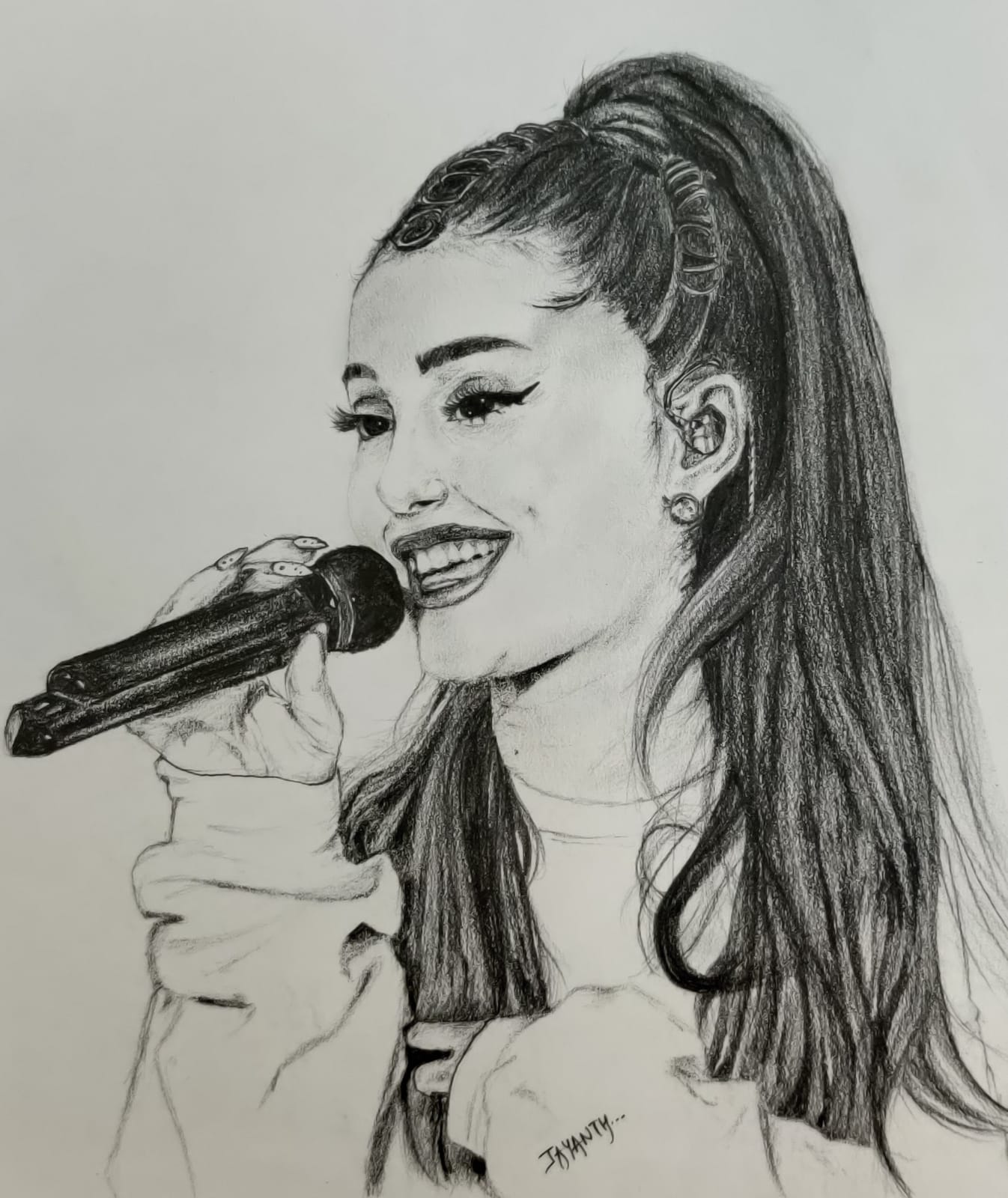

My Artwork

|

Recent Reads'Norwegian Wood' by Haruki Murakami and 'Yolk' by Mary. H. K. Choi. |

Website Template Credits to Rishab Khincha: Source Code.